The IP-core has been validated thanks to the official NIST Statistical Test Suite, in order to evaluate the degree of randomness of the numbers generated in output. Subsequently, specific architecture optimizations were studied to achieve better timing performance and very high throughput values. The specifications used to develop the proposed project were derived from dedicated literature and standards.

This paper presents the architecture of a high performance Random Number Generator (RNG) IP-core, in particular a Cryptographically Secure Pseudo-Random Number Generator (CSPRNG) IP-core, a digital hardware accelerator for random numbers generation which can be employed for cryptographically secure applications. Consequently, any weakness in the key generation process can potentially leak information that can be used to breach even the strongest cipher. Random numbers are in fact used to generate the encryption keys to be used for ciphers. Random number generation is crucial in modern encryption and security applications as it is a critical task from the point of view of the robustness of the security chain.

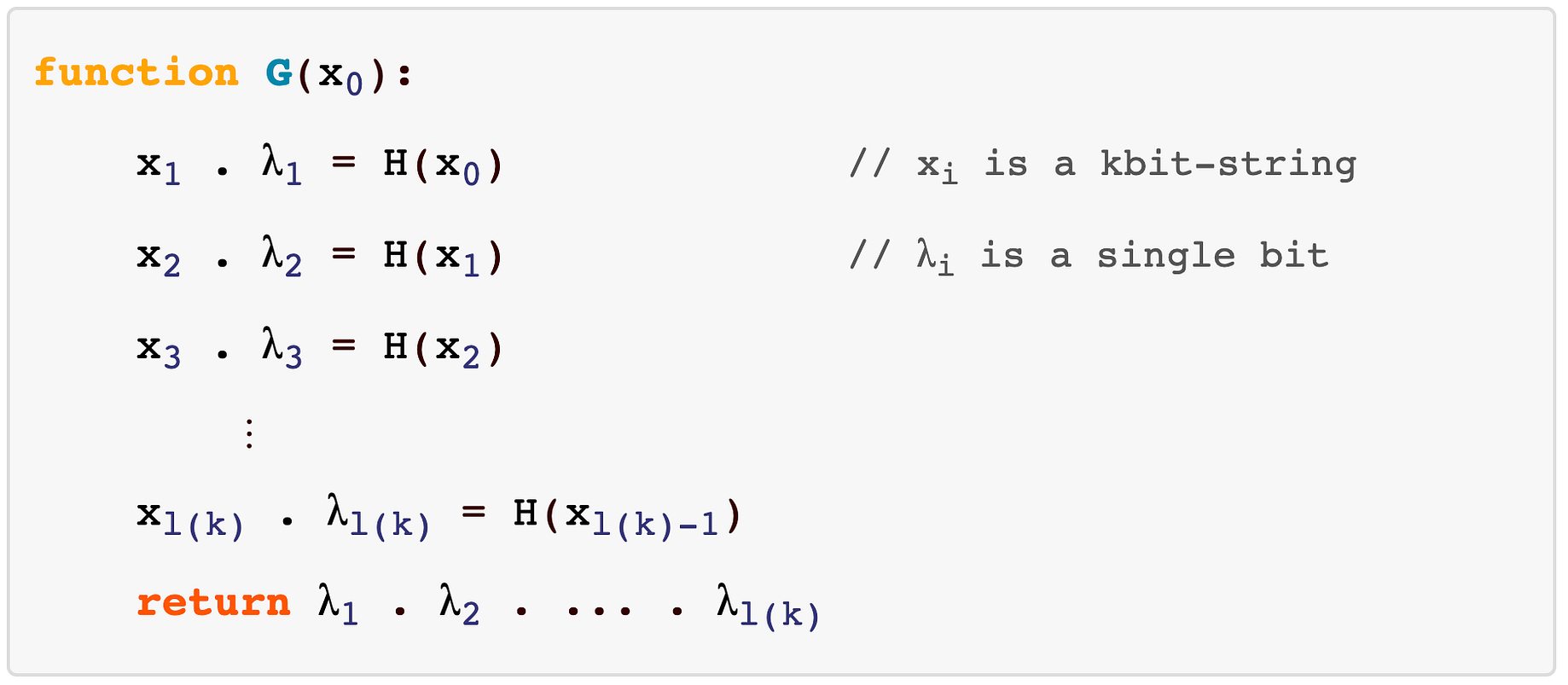

Pseudo random generator algorithm driver#

In the context of growing the adoption of advanced sensors and systems for active vehicle safety and driver assistance, an increasingly important issue is the security of the information exchanged between the different sub-systems of the vehicle.